# Improved RF Modeling Techniques for Enhanced AlGaN/GaN HFETs

S. Nuttinck, E. Gebara, J. Laskar, J. Shealy, and M. Harris

**Abstract**—Modeling procedures of an AlGaN/GaN HFET that incorporate the effects of both a GaN cap layer and an AlN sub-buffer layer are presented. A single off-state measurement method to extract all eight parasitic elements of an enhanced HFET has been successfully applied. In addition, procedures to model the nonlinear drain-to-source current characteristics featuring a kink are described.

**Index Terms**—AlGaN/GaN HFETs, nonlinear modeling, small-signal modeling.

## I. INTRODUCTION

AlGaN/GaN HFETs offer important advantages for high-power microwave applications such as phased array antennas and base stations [1], [2]. Different GaN-based device structures are being considered and researched to improve the transistors reliability and performance. This paper focuses on devices in which a GaN cap layer, and an AlN subbuffer layer have been added to the HFET layer structure with the objective to improve the gate-drain breakdown voltage [3], and the GaN buffer layer quality [4]–[7], respectively. In the studied HFET, the modifications result in a steady kink in the current characteristics. The AlN subbuffer layer is sometimes attributed to be at the origin of this feature [8]. Since an accurate model is essential to fully benefit from the device's high performance in circuit design, parameters extraction and modeling procedures that integrate the effects of the cap-layer and of the subbuffer layer must be implemented. When modeling a device high-frequency and nonlinear characteristics, a precise extraction of its parasitic elements is critical since it influences the determination of the intrinsic elements values. The conventional Cold-FET method [9], [10] used for on-wafer parasitic elements de-embedding requires forward and reverse bias small-signal measurements, as well as a relation for unequivocal determination of the resistive elements. Because of the GaN cap layer, forward biasing the studied AlGaN/GaN HFET's results in a high gate-to-source polarization leading to more delicate extraction procedure. We propose in this paper to extract all eight parasitic elements from a single off-state ( $V_{GS} < V_{TH}$ ,  $V_{DS} = 0$  V) measurement. This technique simplifies the modeling procedures and does not require forward biasing. Very good agreement between the mea-

Manuscript received August 9, 2002; revised October 18, 2002. The review of this letter was arranged by Associate Editor Dr. Arvind Sharma.

S. Nuttinck, E. Gebara, and J. Laskar are with the Yamacraw Design Center, School of E.C.E., Georgia Institute of Technology, Atlanta, GA 30332 USA.

J. Shealy is with Cornell University, School of Electrical Engineering, Ithaca, NY 14853 USA.

M. Harris is with the Georgia Tech Research Institute, Electro-Optics, Environment, and Materials Laboratory, Atlanta, GA 30332 USA.

Digital Object Identifier 10.1109/LMWC.2003.811062

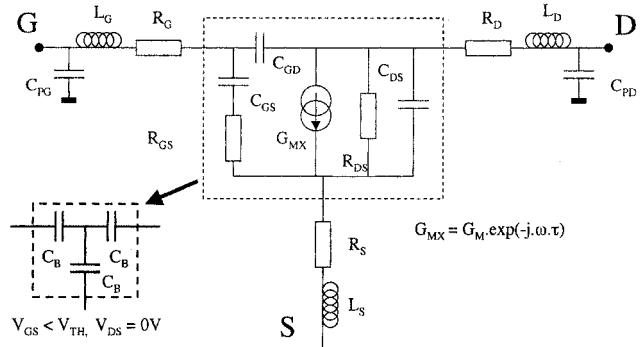

Fig. 1. HFET equivalent circuit model.

sured and the simulated small-signal parameters have been obtained using this modeling method without a final tuning routine. Also, procedures to model the nonlinear current characteristics (kink) are presented.

In Section II the improved method for parasitic elements extraction is successfully applied in the small-signal modeling of an enhanced AlGaN/GaN HFET, and, Section III presents the innovative technique to model the device nonlinear current characteristics featuring a kink.

## II. ENHANCED DEVICE STRUCTURE

The studied transistors are 12-finger devices with a total gate width of 1.5 mm and a gate length of 0.3  $\mu$ m, resulting in a cutoff frequency above 40 GHz. A 50 Å thick GaN cap layer is grown on top of the AlGaN barrier to decrease the gate leakage and improve the breakdown characteristics [3]. Also a 200 nm thick AlN subbuffer layer is grown between the SiC substrate and the GaN buffer to reduce the stress due to lattice mismatch and improve the GaN crystal quality. This results in better device performance and reliability [5]. Power densities in the X-band above 10 W/mm have been reported using similar structures [11].

## III. IMPROVED RF MODELING METHOD

A standard Hybrid-Pi topology (Fig. 1) is used to simulate the small-signal characteristics of an AlGaN/GaN HFET (gate width = 1.5 mm) from 1 GHz to 12 GHz. The elements outside the dotted box represent the extrinsic part of the device. They result from the metal traces and the probing pads.

The method to extract all eight parasitic elements combines the reversed Cold-FET procedure [10], and an LDMOS modeling technique [10]. The “active” part of a pinched-off FET at  $V_{DS} = 0$  V is a depleted region that can be modeled by a

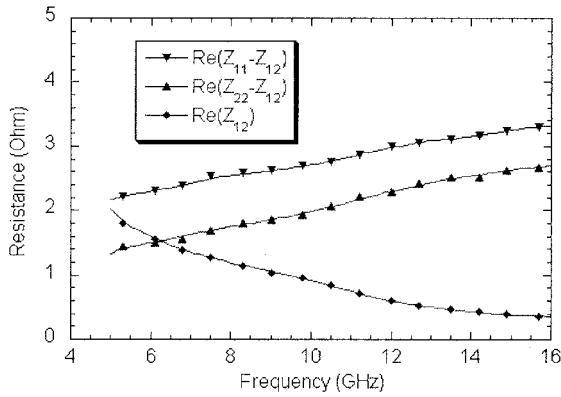

Fig. 2. Extraction procedure for the determination of the resistive parasitic elements values.

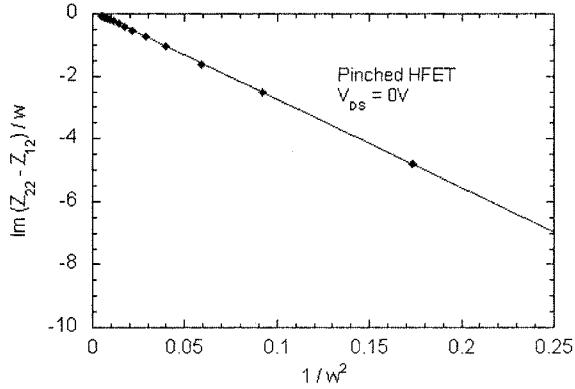

Fig. 3. Extraction procedure for the determination of the inductive parasitic elements values.

symmetric capacitive network (Fig. 1) [11], [12]. This results in simple expressions for the imaginary part of the device's  $Y$ -parameters that are used to extract the pad capacitances ( $C_{PG}$  and  $C_{PD}$ ) [10]. These parasitic capacitances are de-embedded from the measured  $Y$ -parameters, which are converted to  $Z$ -parameters. These  $Z$ -parameters contain the contribution of the parasitic inductive ( $L_S$ ,  $L_G$ ,  $L_D$ ) and resistive ( $R_S$ ,  $R_G$ ,  $R_D$ ) elements, as well as the contribution of the depletion region. They can be expressed through [12]

$$\begin{aligned} Z_{11} - Z_{12} &= R_G + j\omega L_G - \frac{j}{\omega C_B} \\ Z_{22} - Z_{12} &= R_D + j\omega L_D - \frac{j}{\omega C_B} \\ Z_{12} &= R_S + j\omega L_S - \frac{j}{\omega C_B} \end{aligned} \quad (1)$$

where the capacitor  $C_B$  describes the total depletion capacitance under the gate. The real part of these quantities is used to determine the parasitic resistances ( $R_S$ ,  $R_G$ ,  $R_D$ ) (Fig. 2), and the imaginary part is used for parasitic inductive elements ( $L_S$ ,  $L_G$ ,  $L_D$ ) extraction (Fig. 3). In Fig. 2, the measured characteristics to determine the values of the access resistances exhibit a constant drift with frequency of  $\pm 0.1 \Omega/\text{GHz}$ . The resistances values are extracted in the middle of the frequency range.

All 8 parasitic elements being determined, the intrinsic elements can be calculated at any bias points from the intrinsic

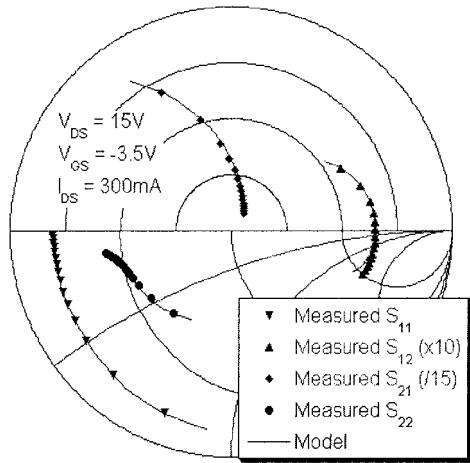

Fig. 4. Comparison between modeled and simulated results from 1 to 12 GHz.

$Y$ -parameters [10], [13]. For the studied device, the extracted parasitic elements are 51 fF, 36 fF, 2.7  $\Omega$ , 2  $\Omega$ , 0.9  $\Omega$ , 65 pH, 71 pH, and 0.2 pH, for  $C_{PD}$ ,  $C_{PG}$ ,  $R_G$ ,  $R_D$ ,  $R_S$ ,  $L_G$ ,  $L_D$ , and  $L_S$ , respectively. The coherency of the method is confirmed by the good agreement between the measured and simulated  $S$ -parameters (Fig. 4).

#### IV. NONLINEAR CURRENT MODELING

In applications where  $f_T$  is well above the frequency of operation, the device current-voltage characteristics dominate its nonlinear behavior [14], making the modeling of the channel current critical for accurate simulation. Nonlinear drain-to-source current ( $I_{DS}$ ) are commonly modeled by [15]

$$I_{DS} = \left( \sum_{k=1}^3 g_k \cdot (V_{GS} - V_{TH})^k \right) \cdot \tanh(\alpha \cdot V_{DS}) \quad (2)$$

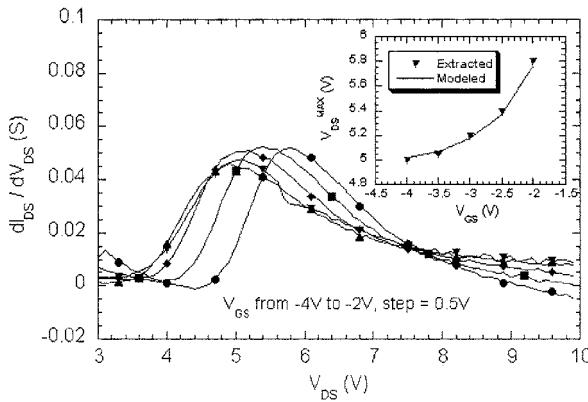

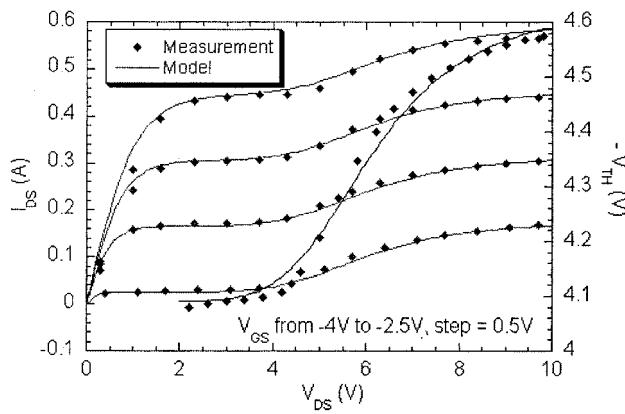

where the polynomial terms contain information about pinch-off and  $I_{DS}$  saturation. For  $V_{GS}$  corresponding to an open channel away from saturation, only the first order term is considered. In this case the device  $I_{DS}(V_{DS})$  characteristics featuring a kink (Fig. 6) can be modeled by considering a bias-dependent threshold voltage ( $V_{TH}$ )

$$I_{DS} = g_0 \cdot (V_{GS} - V_{TH}(V_{DS}, V_{GS})) \cdot \tanh\left(\frac{V_{DS}}{\delta(V_{GS})}\right) \quad (3)$$

where  $g_0$  is a parameter with the units of conductance, and  $\delta(V_{GS})$  is a linear relation that defines the knee of the current characteristics. The case  $V_{TH}(V_{DS}, V_{GS}) = V_{TH}^0 = \text{const}$  corresponds to kink-free current characteristics. By fitting to (3) the part of the current characteristics where  $V_{TH}$  is constant (part of the  $I_{DS}(V_{DS})$  curves on the left side of the kink) it is possible to extract parameters  $g_0$ ,  $\delta(V_{GS})$ , and  $V_{TH}^0$ . Then, subtracting these modeled kink-free characteristics to the measured kinked current characteristics, modeled with (3), leads to the expression of  $V_{TH}(V_{DS}, V_{GS})$

$$V_{TH}(V_{DS}, V_{GS}) = V_{TH}^0 - \frac{\Delta I_{DS}}{g_0 \cdot \tanh\left(\frac{V_{DS}}{\delta(V_{GS})}\right)} \quad (4)$$

Fig. 5.  $dI_{DS}/dV_{DS}$  at various  $V_{GS}$  for  $V_{DS}^{\text{MAX}}$  determination, and extracted and modeled  $V_{DS}^{\text{MAX}}$  parameter.

Fig. 6. Measured and modeled drain-to-source current characteristics.

where  $\Delta I_{DS}$  is the difference between the measured current characteristics (with kink) and the modeled current curves (without kink). Bias-dependent  $V_{TH}$  has an asymmetrical step shape (Fig. 6), and can be modeled by

$$V_{TH}(V_{DS}, V_{GS}) = V_{TH}^0 + \frac{\Delta V_{TH}}{1 + \exp\left(-\frac{V_{DS} - V_{kink}(V_{GS})}{\rho(V_{DS})}\right)} \quad (5)$$

where  $\Delta V_{TH}$  expresses the maximum variation of  $V_{TH}$ ,  $V_{kink}$  determines the position of the step relatively to the drain bias, and  $\rho(V_{DS})$  controls how asymmetric the step is. The variation of  $V_{kink}(V_{GS})$  is similar to the variation of the drain voltage  $V_{DS}^{\text{max}}(V_{GS})$  that maximizes  $(dI_{DS}/dV_{DS})$ . In Fig. 5 we observe that the kink starts at higher values of  $V_{DS}$  when increasing the gate bias. Finally,  $V_{kink}$  is modeled with

$$V_{kink}(V_{GS}) = \alpha + V_{DS}^{\text{max}}(V_{GS}) = \alpha + A + B \cdot \exp\left(\frac{V_{GS} - C}{D}\right). \quad (6)$$

Best fits were obtained for  $\alpha = 1\text{V}$ ,  $A = 4.95\text{ V}$ ,  $B = 0.8\text{ V}$ ,  $C = -2\text{ V}$ ,  $D = 0.8\text{ V}$ .  $\rho(V_{DS})$  is modeled using a linear relation. An optimization routine gives  $\Delta V_{TH} = -0.55\text{ V}$ , and  $\rho(V_{DS}) = 0.24 + 0.14 * V_{DS}$ .

Fig. 6 shows extracted and modeled data for the threshold voltage. Finally the model of the threshold voltage is used to calculate the drain current using (3). The simulated current characteristics agree well with the measured data over the bias range where self-heating is not dominant (Fig. 6).

The fitting equations used in the model not only accurately predict the drain-to-source current characteristics, but enable derivation with respect to  $V_{GS}$  and  $V_{DS}$ , that is crucial for prediction of the fundamental frequency, of the harmonics generation, and of the power added efficiency, under large signal operation.

## V. CONCLUSION

A single off-state measurement method that does not require any current flowing between the gate and the source has been successfully applied to accurately extract all the parasitic elements in equivalent circuit RF modeling of an enhanced AlGaN/GaN HFET. In addition, procedures to model the nonlinear drain-to-source current characteristics featuring a kink are described.

## REFERENCES

- [1] N. Q. Zhang, S. Keller, G. Parish, S. Heikman, S. P. DenBaars, and U. K. Mishra, "High breakdown GaN HEMT with overlapping gate structure," *IEEE Electron Device Lett.*, vol. 21, Sept. 2000.

- [2] S. T. Shepard, K. Doverspike, W. L. Pribble, S. T. Allen, J. W. Palmour, L. T. Kehias, and T. J. Jenkins, "High-power microwave GaN/AlGaN HEMT's on semi-insulating silicon carbide substrates," *IEEE Electron Device Lett.*, vol. 20, pp. 161–163, Apr. 1999.

- [3] T. Kikkawa, M. Nagahara, T. Kimura, S. Kato, M. Yokoyama, Y. Tateno, K. Horino, K. Domen, Y. Yamaguchi, and K. Joshi, "A 36W CW AlGaN/GaN-power HEMT using surface-charge-controlled structure," in *IEEE MTT-S Dig. 2002*, pp. 1815–1818.

- [4] H. Kim, V. Tilak, B. Green, H. Cha, J. A. Smart, J. R. Shealy, and L. F. Eastman, "Degradation characteristics of AlGaN/GaN high electron mobility transistors," in *IEEE 39th Annu. Int. Reliability Physics Symp.*, Orlando, FL, 2001, pp. 214–218.

- [5] S. Nakamura, "In-situ monitoring of GaN growth using interference effects," *Jpn. J. Appl. Phys.*, vol. 30, no. 8, pp. 1620–1627, Aug. 1991.

- [6] H. Amano, N. Sawaki, I. Akasaki, and Y. Toyoda, "Metalorganic vapor phase epitaxial growth of a high quality GaN film using an AlN buffer layer," *Appl. Phys. Lett.*, vol. 48, no. 5, pp. 353–355, Feb. 1986.

- [7] J. A. Smart, A. T. Schremer, N. G. Weimann, O. Ambacher, L. F. Eastman, and J. R. Shealy, "AlGaN/GaN heterostructures on insulating AlGaN nucleation layers," *Appl. Phys. Lett.*, vol. 75, no. 3, pp. 388–390, July 1999.

- [8] S. Nuttinck, E. Gebara, J. Laskar, and M. Harris, "Floating-body effect in AlGaN/GaN power HEMT," in *GAAS 2002 Dig.*

- [9] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small-signal equivalent circuit," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 1151–1160, July 1988.

- [10] P. White and R. Healy, "Improved equivalent circuit for determination of MESFET and HEMT parasitic capacitances from "ColdFET" Measurements," *IEEE Trans. Microwave Theory Tech.*, vol. 3, pp. 453–455, July 1993.

- [11] L. Eastman, "Experimental power-frequency limits of AlGaN/GaN HEMT's," in *IEEE MTT-S Dig.*, 2002, pp. 2273–2275.

- [12] R. Gaddi, P. J. Tasker, and J. A. Pla, "Direct extraction of LDMOS small signal parameters from off-state measurements," *Electron. Lett.*, vol. 36, no. 23, pp. 1964–1966, Nov. 2000.

- [13] M. Berroth and R. Bosh, "Broad-band determination of the FET small-signal equivalent circuit," *IEEE Trans. Microwave Theory Tech.*, vol. 38, pp. 891–895, July 1990.

- [14] P. Ladbrooke and J. Bridges, "Current-voltage characteristics of FET's, HEMT's and bipolar transistors in contemporary circuit design," *Microwave J.*, vol. 45, no. 3, March 2002.

- [15] S. Maas, *Nonlinear Microwave Circuits*. Norwood, MA: Artech House, p. 66.